电容测试法在PCB电性能测试中的应用研究 发布时间:2021-06-30

摘要

在PCB电性能测试中,测试方法多种多样,而电容测试法是一种很重要的手段。文章从电容的基本原理入手,引入电容测试法在PCB电性能测试中的应用。通过与普通的开短路测试法进行对比,找出电容测试法的优势,并以实际案例进行分析,体现出电容测试法在PCB电性能测试中的重要作用。

1. 前言

随着电子产品、工控、航天等行业的高速发展,PCB产品的电性能要求越来越高,同样,我们电测试的难度也越来越大。对于PCB厂商来说,面对大批量产品,我们主要选用夹具针床测试,虽然有制作夹具的成本,但可以大大节省测试时间。而面对样品、小批量产品以及图形密集的HDI产品,我们主要选用飞针测试,一方面可以节省夹具制作成本,另一方面,在精细节距的BGA或MBGA中,夹具测试不能保证其测试精度,所以飞针测试是一个企业不可或缺的测试手段。我们常见的飞针测试法为开短路测试法,也叫电阻测试法,此种方法可满足精密线路测试,但测试时间偏长,需要进行开路和短路两次测试,测试一片产品往往需要10分钟以上的时间,测试效率很低。进而,我们引进电容测试法来改变此现状。

2. 电容测试法简介

2.1 电容的基本原理

电容测试法是根据电容的基本原理进行开短路测试。电容计算公式为:

C=εS/4πd。其中C是电容的容量;ε是介电常数,由绝缘介质的材质决定,介质不变则为恒定值;S是两极板之间相对重叠部分的垂直面积d是两极板之间的距离。

2.2 电容测试法的基本原理

如图1所示,在电容测试法中,根据电容计算公式,绝缘介质ε为板材介电常数,两极板的一极是整个大的测试台面,另一极则是测试网络的铜面,因而S值取决于测试网络的铜面积大小;d在同一型号产品时板厚也为恒定值。由此可以看出,在电容测试法中,电容值的大小最终取决于测试网络的铜面积大小,并与其成正比,所以该方法也叫静电容量比较法。

图1 PCB产品电容测试示意图

2.3 电容测试法开短路的判定方法

2.3.1 电容测试法开路的判定方法

如果导电图形中出现断路,则导电图形面积就会减少,静电容量值也会变小。例如图2所示,合格产品中端点1和端点2所测的静电容量值为100,而断路产品中端点1和端点2所测的静电容量值分别为70和30。通过导电图形面积的变化,可准确检查出图形中断路位置。

图2 电容测试断路示意图

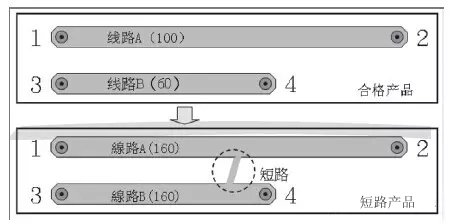

2.3.2 电容测试法短路的判定方法

如果导电图形中出现短路,则导电图形面积就会增加,静电容量值也会变大。例如图3所示,合格产品中端点1和端点2所测的静电容量值为100,端点3和端点4所测的静电容量值为60,而短路产品中端点1、2、3、4所测的静电容量值都为160。通过导电图形面积的变化,可准确检查出图形中短路位置。

2.3.3 电容测试法开短路的现场模拟

如图4所示,为我司飞针电容测试模拟图,我司采用的是水平式电容飞针电容测试,可对较薄的基板起到良好的吸附作用,基板上的导电图形与在电性能上检查用的电极(Sensor Board)之间,存在与其图形面积成正比的静电容量,假设我们对线路端点A、B、C、D、E、F、G、H、I、J、K、L、M测定的静电容量为:A = C = H = K = L = 100,B = 10,D = G = M = 90,E = F = 30,I = J = 30。

图4 电容测试现场模拟图

当图形线路发生断路时,如图5所示,测定的静电容量为:A = C = H = 70,B = 10,D = 20,E = F = 30,G = M = 70,I = J = 30,K = L = 30。我们可发现,A、C、H、K、L、D、G、M的电容值变小,可确定这几个端点所在网络发生断路。

图5 电容测试断路模拟图

当图形线路发生断路时,如图6所示,测定的静电容量为:A = C = H = K = L =100,B = 10,D = E = F = G = M = 120,I = J = 30。我们可发现,D、E、F、G、M的电容值变大,可确定这几个端点所在网络发生短路。

图6 电容测试短路模拟图

3.电容测试法与普通电阻测试法的对比

电阻测试法,是通过测量两点间阻抗的方法,需要确认同一网络内端点间的导通以及不同端点间的非导通。因为要确认不同线路间全部组合的非导通情况,所以检查数量非常多。而电容测试法,是通过一次测定全线路端点的静电容量(面积),可以同时进行短路和断路的确认,因此检查数量比一般的检测方式大幅度减少,有时可以减少90%以上。

举个例子,当线路总数为100,端点总数为500时,我们对电阻测试方式与电容测试方式的测试次数进行对比,如表1所示,电阻法的测试总次数为5350次,而电容法的测试总次数只有500次,从这个例子我们可看出,电容测试法在测试时间上有很大的优势。

如表2所示,为我司电容测试对某一产品的检测时间,此产品线路总数为364,端点总数为1207,独立焊盘个数为124,单台设备有两个测针探头,可同时测试两片产品。

从数据中我们可以看出,电容测试法同时测试两片产品所需时间为119s,相当于测试一片产品所需时间为1分钟,而普通开短路测试,只非导通测试就需364×(364-1)/2=66066 step,加上导通测试时间,测试一片产品至少需要20分钟,是电容法测试时间的20倍以上。

4.电容测试法在PCB电性能测试中的特殊作用

众所周知,电容测试法与电阻测试法的检测效果是一样的,都是对产品中每一网络的通断进行测试,但是,这两种测试方法的检测原理不同。那么我们可不可以对电容测试法的特殊检测原理加以利用呢?

通常,在电性能测试后,我们会对不良品进行分析,总的来说,缺陷可分两大类:短路与断路。而这两种缺陷中,我们更侧重于对断路的分析,因为断路位置有可能发生在线上,也有可能发生在孔内。当断路位置发生在孔内,就必须确认造成孔断的原因,当孔断原因为批量因素时,那么整批产品都存在失效的隐患,特别是HDI产品,盲孔所在网络占很大比例,一旦盲孔出现异常,将面临整批产品的报废。如图8所示,为HDI产品电性能测试中,出现断路缺陷的三种主要来源。

图7 电性能测试断路缺陷来源示意图

对于一批发生断路的HDI产品,其断路原因可能为上述一种,也可能上述三种原因都存在,如果断路原因之一为盲孔断路,那么此批产品就要具体分析,并将盲孔断路的原因找出,以此来判断整批产品焊接时是否有失效的风险。然而,如何确定盲孔断路是一个复杂的过程。普通的电阻测试法,只能确认某一或某些网络发生断路,要想确认盲孔,需对该网络内的所有盲孔位置进行切片,如果断路产品数量很多,则需对所有断路产品逐片切片进行分析,这将花费很长的时间。

这时,我们可利用电容测试法对HDI产品进行电性能测试。通常情况下,HDI产品网络的起始端点都为盲孔,当盲孔发生断路时,该点的电容值很小,不会超过1fF,而正常导通的网络中,整个网络电容值在几百到几千fF。通常,我们对断短路的判定标准为:当测试电容值>(1+20%)标准电容值,判定为短路,当测试电容值<(1-20%)标准电容值,判定为断路。当线路发生断路时,所测电容值至少也会在几十到几百fF。所以,我们只需对小于1fF电容值的盲孔位置进行切片即可,此位置必定为盲孔断路。这种方法可大大减少我们的分析时间,同时在做切片之前,就可对盲孔断路数量及所占比例做出初步判断。

某公司司曾经生产的某一HDI产品,整批产品采用电容法测试,最终检测出5片断路产品,其中有两片为端点电容值小于1fF,对这两片产品的端点盲孔进行切片,可确认为盲孔断路,对缺陷原因进行分析为粉尘堵孔,此现象为个量问题,其余合格产品可放行。从测试—分析—判定,此产品仅用了很短的时间,大大减少了产品的生产周期,提高了生产效率。

某公司曾经生产的另一HDI产品,同样为采用电容法测试,最终检测出20片断路产品,其中有8片为端点电容值小于1fF,对其端点盲孔进行切片,可确认为盲孔位置断路,缺陷原因为埋孔堵孔不实,从而导致了盘中孔位置镀铜凹陷,致使激光钻盲孔未打到底铜。此类问题对产品的电性能有很大隐患,极容易造成盲孔与埋孔的微连接,所以,此批电测试产品,无论合格与否,全部报废处理。正是因为电容测试法的高效性与准确性,为我们快速而准确的分析出了此问题,也为我们重新制作这批产品赢得宝贵时间。

通过以上两个案例,我们可发现,利用电容测试法测试HDI产品,可快速的检测出盲孔断路位置,减少了我们对产品的分析时间,进而提高了生产效率。另一方面,电容测试法可准确定位不良盲孔所在的位置,通过切片能一针见血的找到问题所在,然后根据问题产生的原因,及时制定改善措施,从而避免此类问题的发生。

5.结论

(1)电容测试法对导电图形静电容量的测试主要取决于导电图形的面积。如果导电图形中出现断路,则导电图形面积会减少,静电容量值也会变小。如果导电图形中出现短路,则导电图形面积会增加,静电容量值也会变大。

(2)电容测试法是对导电图形的面积进行测试,可开短路同时进行,并且电容测试机的两个探针可对两片产品同时测试,在测试时间上比普通电阻测试法快很多倍。

(3)电容测试法在HDI产品的电性能测试中起特殊作用,若起始盲孔端点发生断路,则该点的电容值极小,可直接确定该网络中的断路位置为此盲孔。而电阻测试法只能测出一个网络发生断路,不能直接判定某一线断还是孔断,需做大量切片进行分析。因而电容测试法可广泛用于HDI产品的电测试中。

- 上一篇: PCB/PCBA失效分析

- 下一篇: x-ray检测技术对SMT工艺的作用